输入输出系统介绍

作用、功能

与其他系统的关系

输入/输出系统组成

要解决的问题

控制方式

- CPU 如何控制输入/输出?(输入/输出方式)

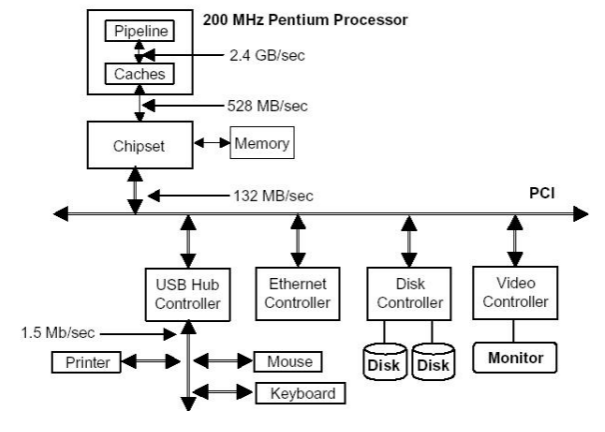

传输方式

- 传输通道、方式、速率等(总线、接口)

数据识别和转换

- 数/模转换、语音识别等,转换为字符、数据等计算机能 识别的格式(设备)

输入/输出方式

程序直接控制

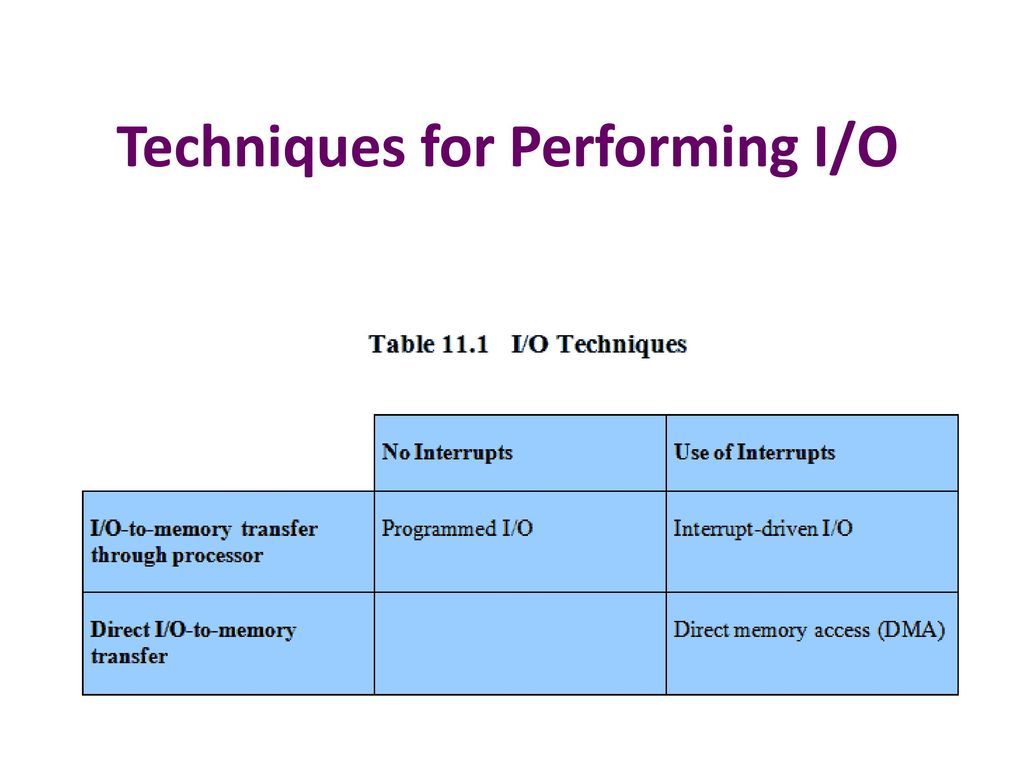

I/O 技术分类

- 程序控制 I/O:处理器代表进程给 I/O 模块发送 I/O 命令,该进程忙等待直到操作完成;

- 中断驱动 I/O:处理器代表进程给 I/O 模块发送 I/O 命令,若 I/O 指令是非阻塞的,则处理器继续执行 I/O 命令的后续指令;若是阻塞的,则处理器执行的下一条指令来自 OS,将当前进程设置为阻塞态并调度其它就绪进程;

- 直接内存访问 DMA:DMA 模块控制内存和 I/O 模块之间的数据交换,为传送一块数据,处理器给 DMA 模块发送请求,且只有整个数据块传送结束后才向 CPU 发送中断请求

指向原始笔记的链接

操作:

- CPU 方:

- 查询接口状态(循环等待)

- 直到接口已经接收到该字符

- 读字符

- 外设方:

- 往接口数据缓冲中送字符处理完后,置状态寄存器 等待下一个字符

程序直接控制方式特点

- 成本低

- 效率低

- 严重占用 CPU 资源

- 适用情况:早期计算机中高速设备

中断

程序中断方式

- CPU 和外部设备同时工作

- 外部设备发起请求

- CPU 暂停正在执行的程序,进行响应

- 处理完成后,继续执行原来的程序

- 提高 CPU 的效率

- 可以同时管理多个外部设备

中断源

- 外中断:I/O 设备等

- 异常 (内中断):处理器硬件故障、程序“出错” ,Trap

- 中断触发器

- 中断状态寄存器

中断优先级: 响应中断的顺序

禁止中断与中断屏蔽

- 中断允许触发器(EI、DI)

- 有选择封锁

中断的完整过程:

- 中断请求

- 中断源设备设置中断触发器

- 每个中断源有 1 个中断触发器

- 同时可设置 1 个中断屏蔽触发器

- 中断源设备设置中断触发器

- 中断响应

- 响应条件:允许中断、当前指令结束、优先级

- 响应实现:硬件实现的中断隐指令,保存断点

- 中断处理

- 保存现场信息

- 运行中断服务程序

- 中断返回

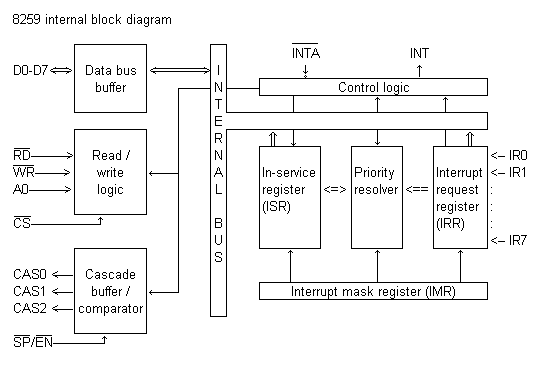

8259A 中断机制

- 中断请求寄存器: Interrupt Request Register

- 中断屏蔽寄存器: Interrupt Mask Register

- 优先级排队线路: Priority resolver

- 数据缓冲寄存器: Data bus buffer

- 中断控制和工作状态逻辑: Control logic

- 设备选择器:

- 中断向量表: Int-service Register

应用场景与特点

程序中断方式应用场景:

- CPU 与外部设备并行工作

- 硬件故障处理

- 人机交互

- 多道程序和分时操作

- 实时处理(监控)

- 应用程序和操作系统之间的联系

- 多处理机中各处理机之间联系

中断控制方式特点

- 适用情况

- 传输速度不高

- 传输量不大

- 对 CPU 干扰较大

DMA

Circular transclusion detected: 1-Theory/3-System/03-Operating-System/Internal-and-design-principle/60-IO管理与磁盘

I/O 设备和主存储器之间的直接数据通路,为专设的硬件,用于高速 I/O 设备和主存储器之间成组传送数据。

- 数据传输过程由 DMA 自行控制

- 主存储器需要支持成组传送

- 数据传送开始前和结束后通过程序或中断方式对 DMA 进行预处理和后处理

- DMA 工作方式

- 独占总线方式:当外设要求传送一批数据时,由 DMA 控制器发一个信号给 CPU。DMA 控制器获得总线控制权后,开始进行数据传送。一批数据传送完毕后,DMA 控制器通知 CPU 可以使用内存,并把总线控制权交还给 CPU。

- 周期窃取方式:当 I/O 设备没有 DMA 请求时,CPU 按程序要求访问内存:一旦 I/O 设备有 DMA 请求,则 I/O 设备挪用一个或几个周期。(随时,一旦冲突,DMA 优先)

- DMA 与 CPU 交替访问内存总线:一个CPU周期可分为2个周期,一个专供DMA控制器访内,另一个专供CPU访内。不需要总线使用权的申请、建立和归还过程。

DMA 实现时的问题

虚拟地址和实地址

- DMA 若采用实地址:虚拟地址连续,但实地址不连续

- 若采用虚拟地址:DMA 需要进行虚实地址转换

Cache 一致性:

- 主存中的数据可能不是最新的

- 采用直接写会带来性能的降低

- DMA 查询 Cache,降低性能

- 直接设计硬件控制

特点

- 与设备一对一服务

- 多 DMA 控制器同时工作可能发生冲突

- 对 CPU 打扰适中

- 初始化

- 周期挪用

- 无法适用大量高速设备的管理

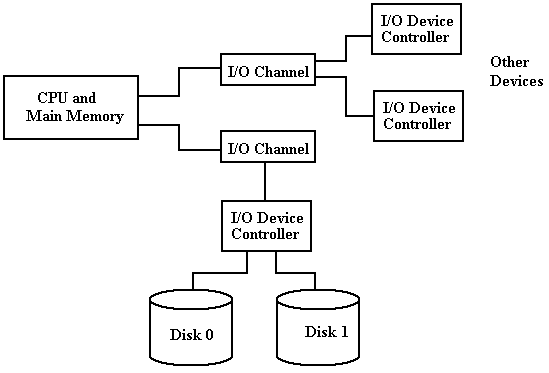

通道

I/O 通道是计算机系统中代替 CPU 管理控制外设的独立部件,是一种能执行有限 I/O 指令集合——通道命令的 I/O 处理机。

- 一对多的连接关系

- 适应不同速度、不同种类的外部设备,可并行工作。

Circular transclusion detected: 1-Theory/3-System/03-Operating-System/Internal-and-design-principle/60-IO管理与磁盘

功能

- 根据 CPU 要求选择某一指定外设与系统相连,向该外设发出操作命令,进行初始化

- 指出外设读/写信息的位置以及与外设交换信息的主存缓冲区地址

- 控制外设与主存之间的数据交换

- 指定数据传送结束时的操作内容,检查外设的状态

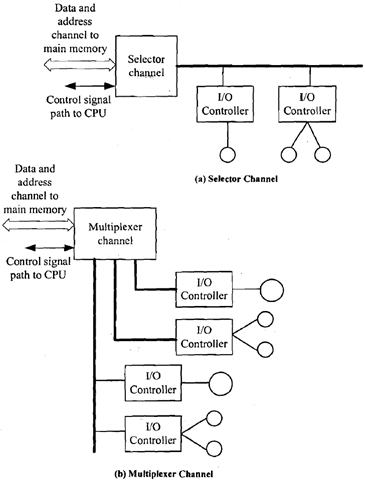

通道的类型

- 字节多路通道

- 简单的共享通道,分时处理,面向低、中速字符设备

- 选择通道

- 选择一台外设独占整个通道,以成组传送方式传送数据块,效率高,适合快速设备

- 数组多路通道

- 上两种方式的结合,效率高,控制复杂

外围处理机

- 通道型处理机

- 共享内存

- 外围处理机

- 通用计算机

- 独立完成输入/输出功能

- 通过通道方式与主机进行交互

设计 I/O 系统

考虑的因素:

- 性能

- 考虑吞吐量和延迟

- 适应各种不同类别的设备的性能的差异

- 从操作系统、驱动程序等各方面综合考虑

- 考虑到设备性能的提高

- 可扩展性

- 允许更多的设备接入到输入/输出系统

- 可适应性

- 设备有无

- 设备故障

输入/输出系统的目标:

- 输入/输出设备多,功能复杂,速度不一

- 多种控制方式,解决速度不一的问题,尽量少地占用 CPU 资源

- 操作系统管理

- 硬件直接支持

- 与不同的设备有直接的依赖关系(驱动程序)

- 尽量使设备使用统一的标准——虚拟设备 virtio